门电路_TTL¶

约 2947 个字 38 张图片 预计阅读时间 15 分钟

内容总览

- TTL集成门电路

TTL集成门电路¶

集成电路:Integrated Circuit(IC)

TTL电路是晶体管-晶体管逻辑电路(Transistor-Transistor-Logic),TTL电路是数字集成电路的一大门类。它采用双极型工艺制造,具有高速度低功耗和品种多等特点

TTL与非门¶

TTL与非门的结构¶

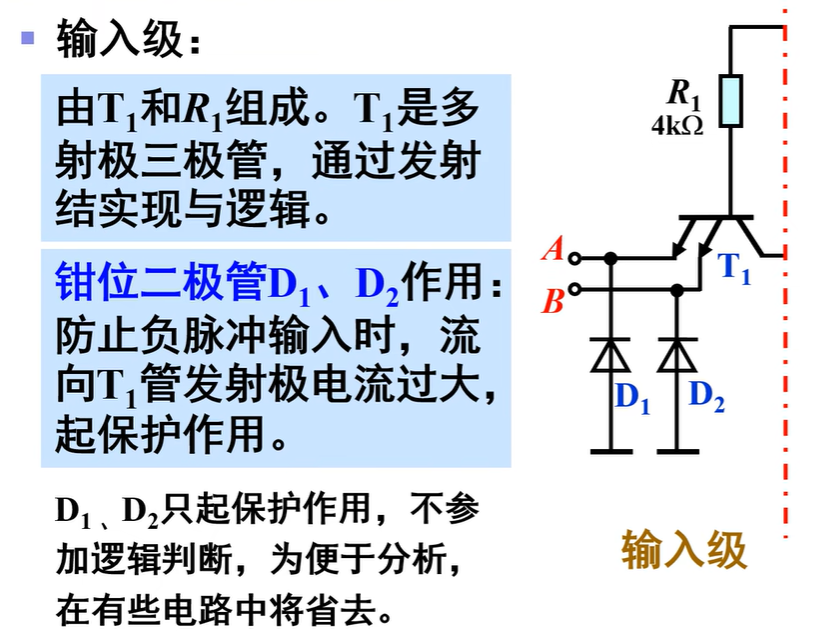

- 输入极

\(T_1\)其实就可以看作两个三极管,基极和集电极都接到一起了,发射极分别接出

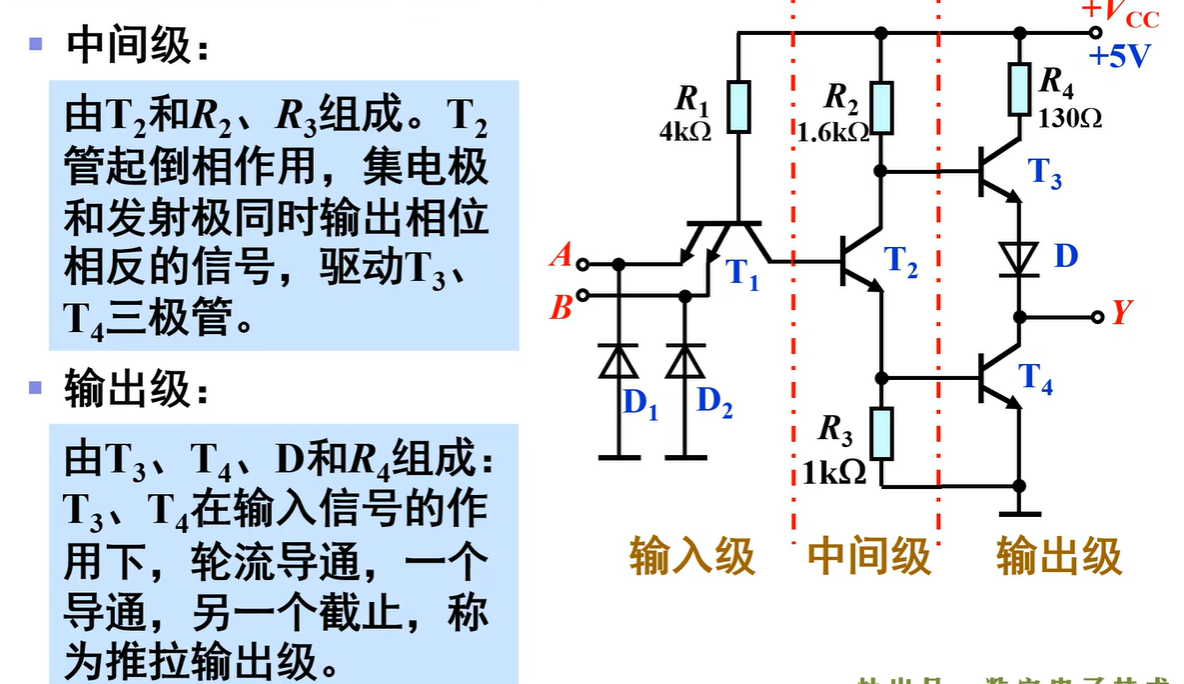

- 中间极和输出极

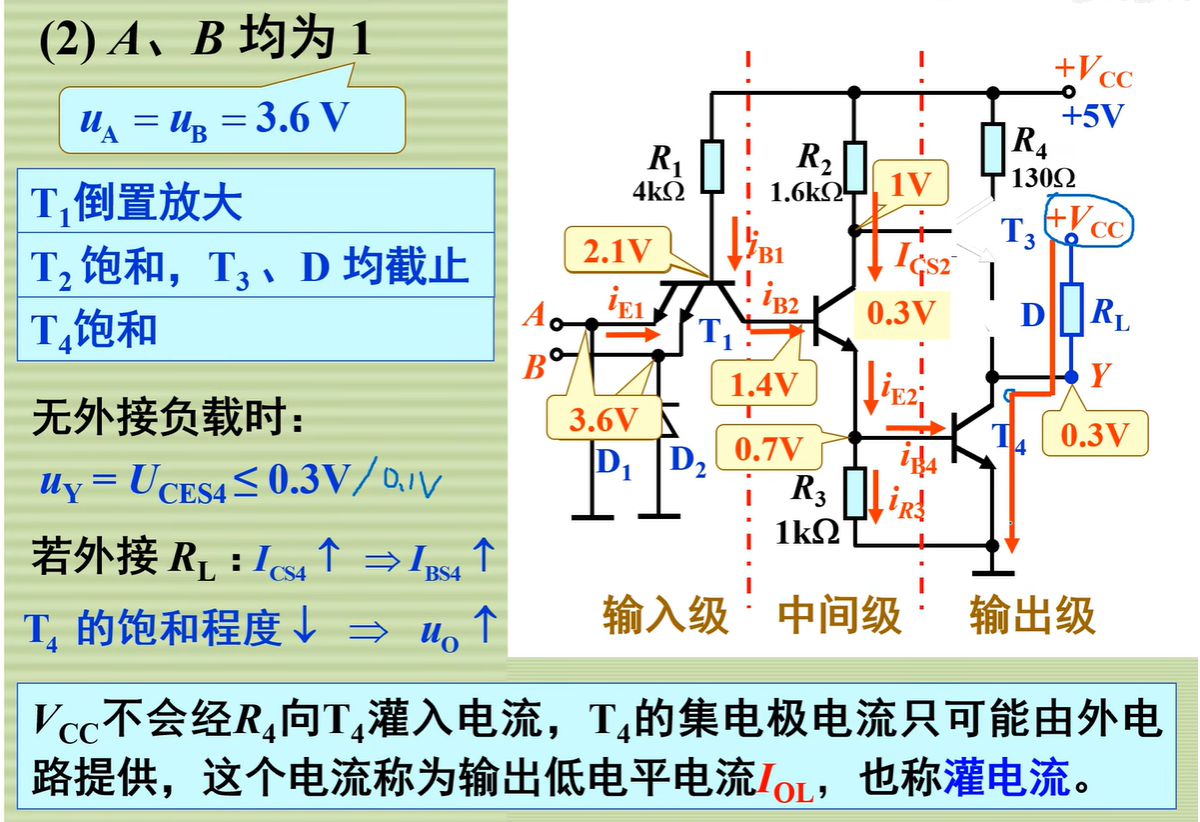

TTL与非门的工作原理¶

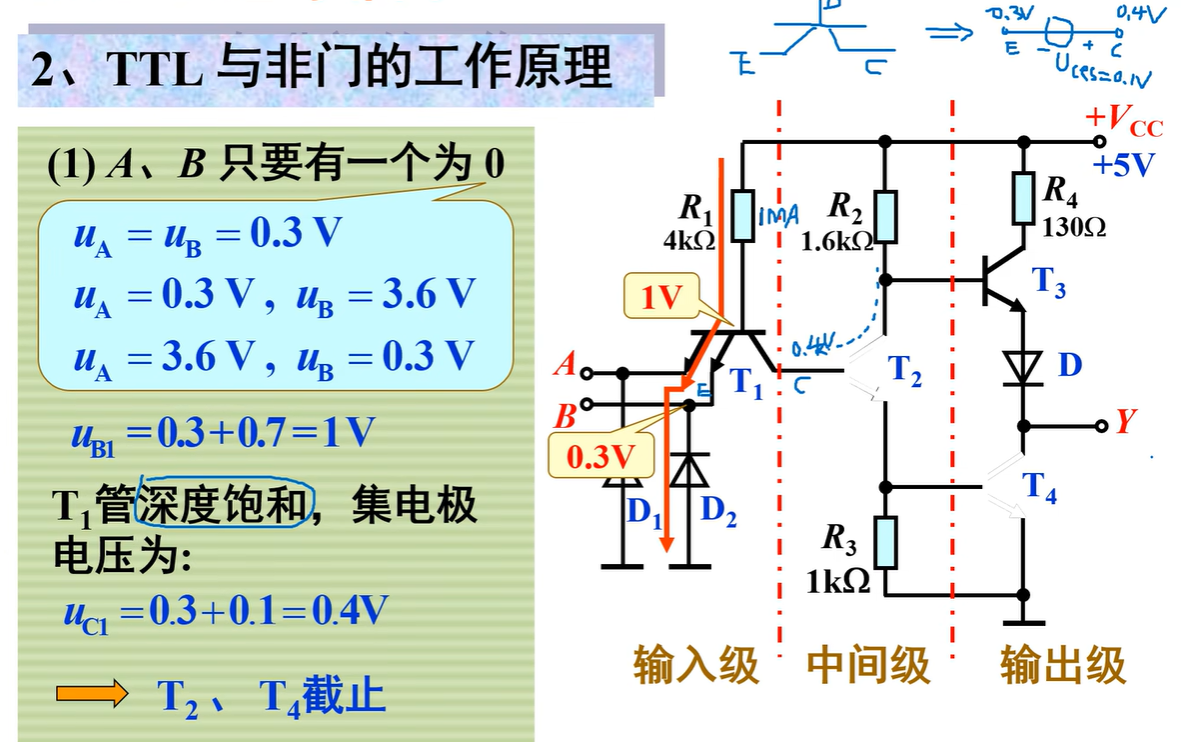

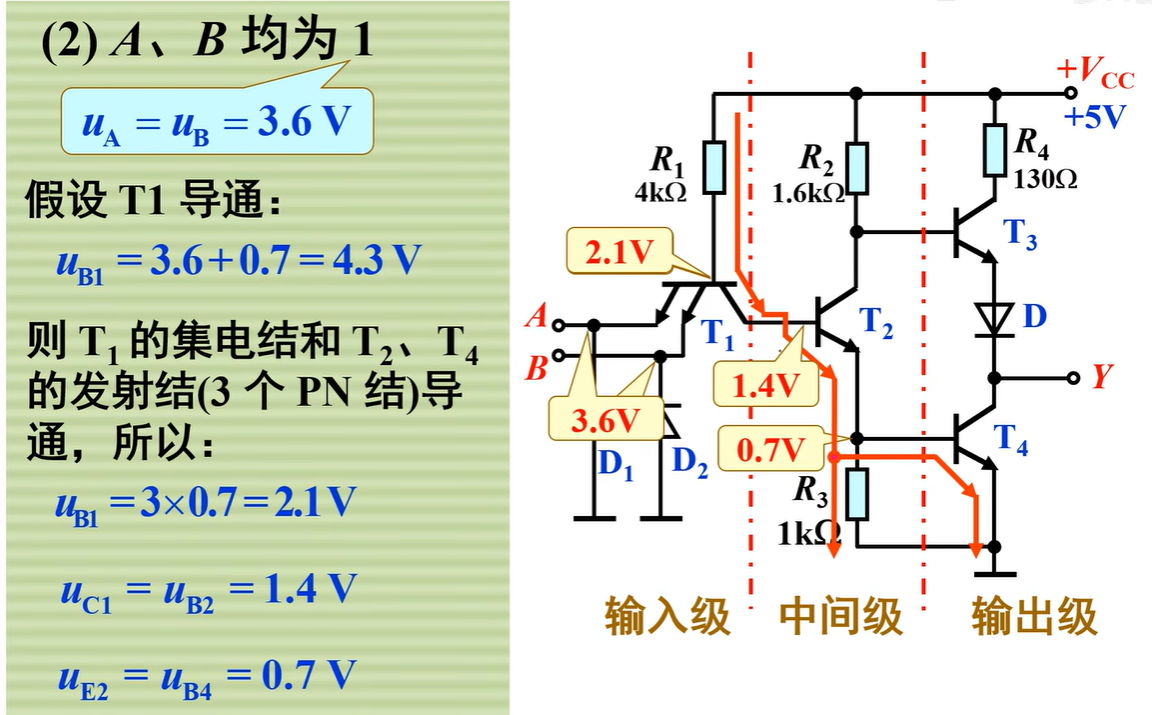

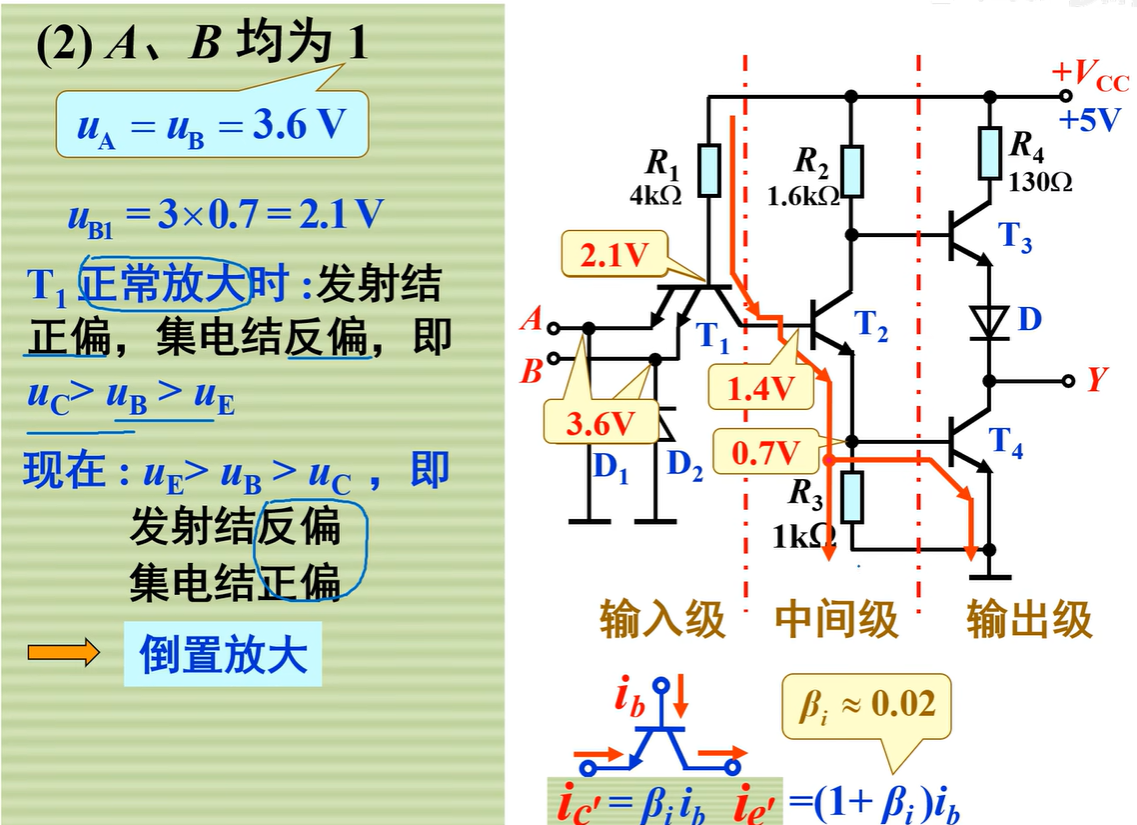

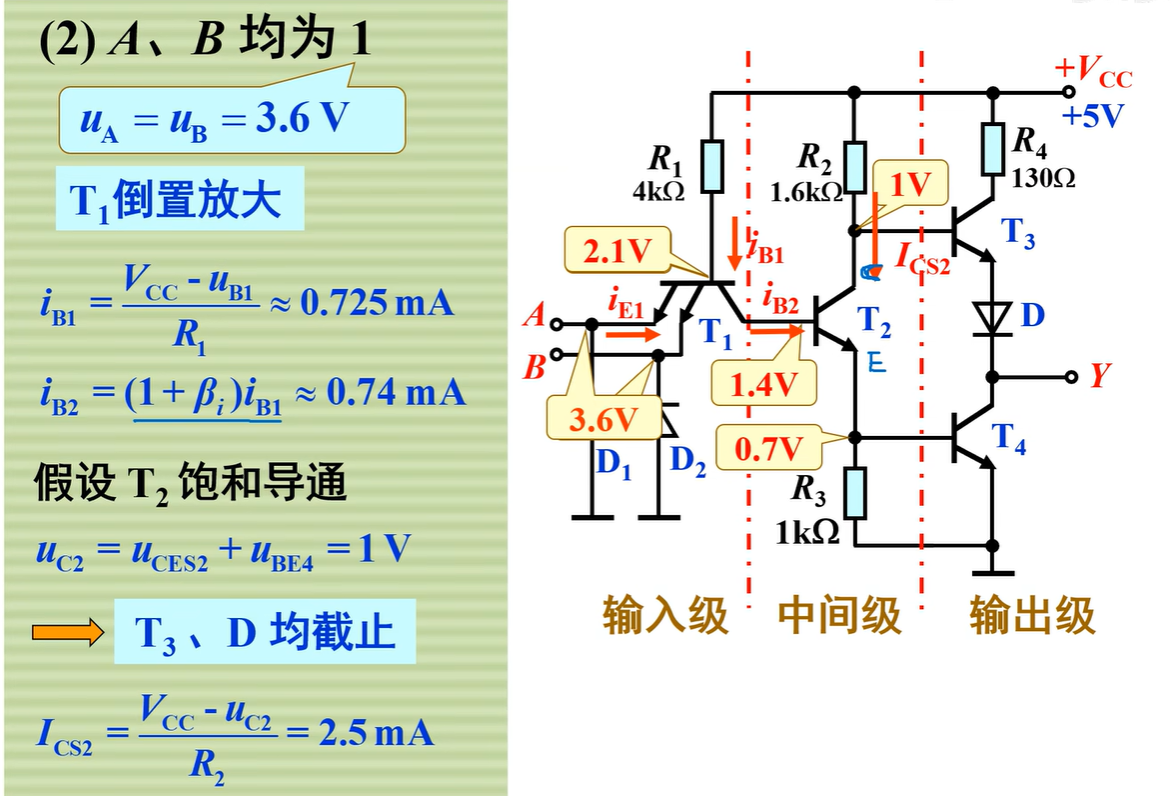

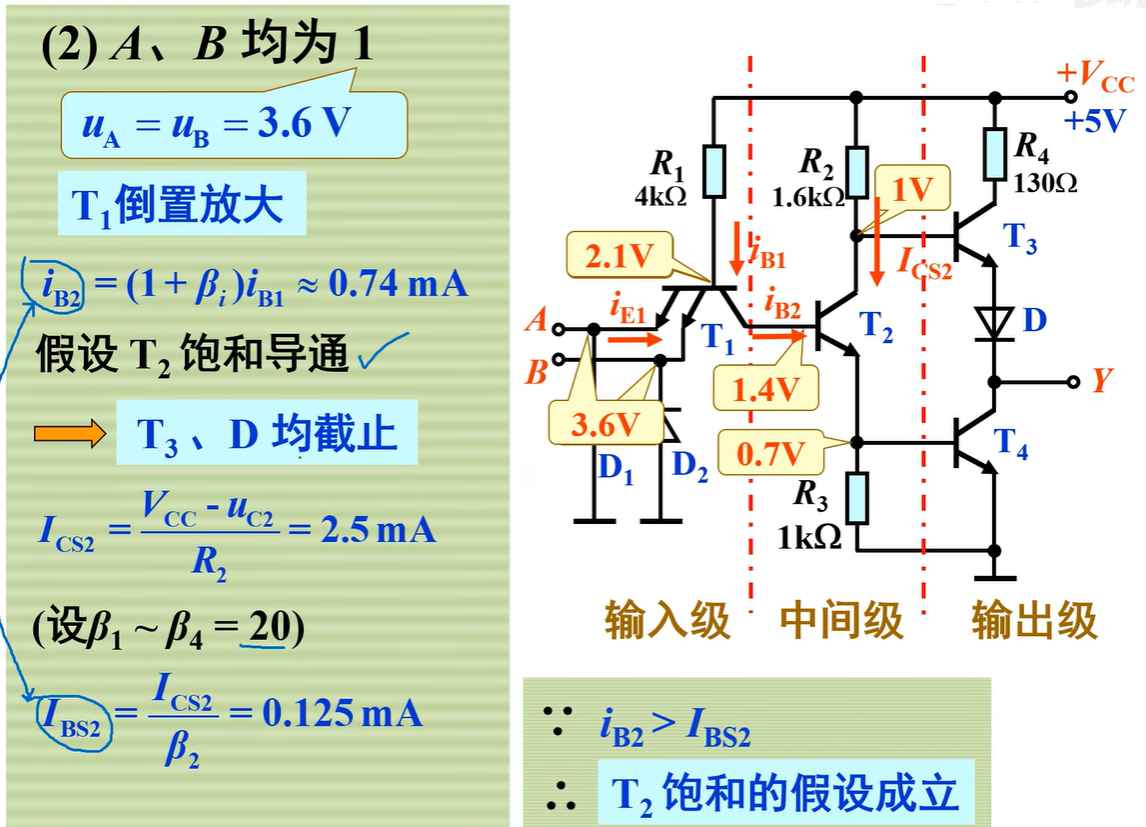

规定:输入低电平取0.3V,高电平取3.6V,二极管导通电压0.7V,三极管导通发射结电压0.7V,饱和导通三极管电压\(U_{CE}\)为0.3V

三极管的深度饱和状态:饱和后,集电极电流和基极电流不再成\(\beta\)的关系,基极电流很大(有时比集电极电流还大),就会进入深度饱和状态,进入深度饱和状态后,\(U_{CE}\)就不再认为是0.3V而是0.1V

注:关于判断深度饱和,先得出\(u_{B1}\)为1V,得到\(I_{R1}\)为\(1mA\),这个电流其实是算比较大了,故可认定该三极管工作在了深度饱和状态下,则可以得到\(u_{C1}=0.3+0.1=0.4V\),达不到\(T_2\)管的导通所需基极电压(0.7V),而\(T_4\)是由\(T_2\)来控制的,故可认定\(T_2\)和\(T_4\)截止,也就是断开

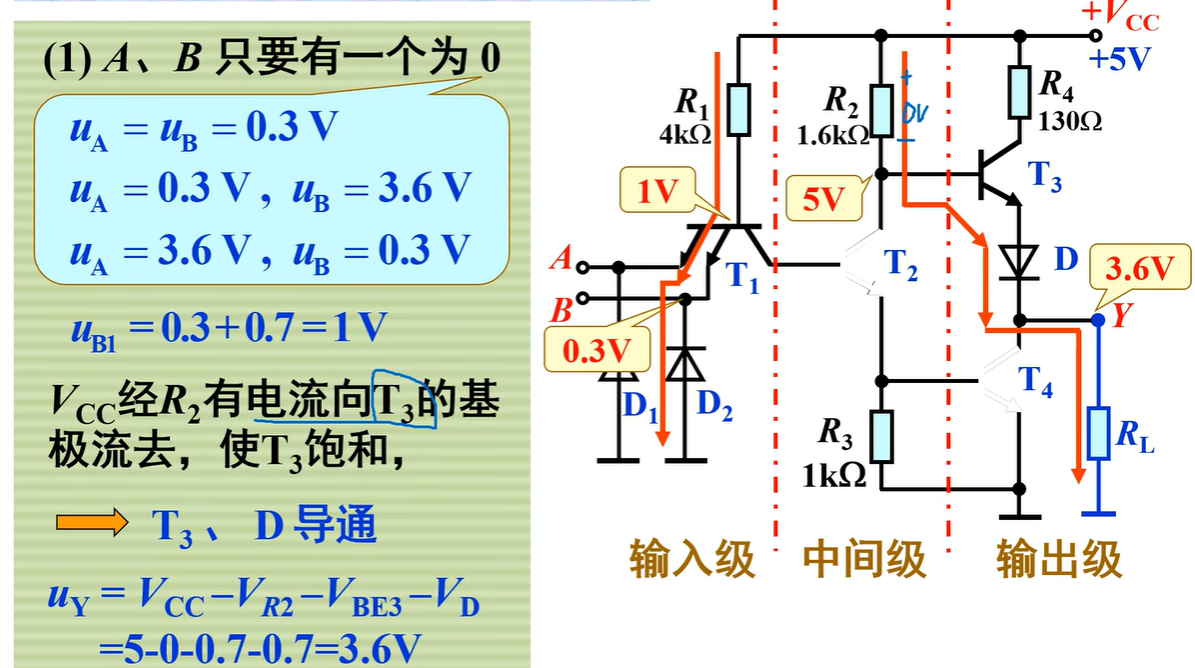

注:为什么\(T_3\)基极是5V?因为\(T_3\)是饱和导通的,则\(T_3\)发射极会有电流向下流,但是\(T_4\)是截止的,只能有一点点的电流(即穿透电流)通过\(T_4\),故而上图中说\(V_{CC}\)经\(R_2\)有电流流向\(T_3\)的基极,但是很小,所以认为\(R_2\)两端压降是0V

外接负载\(R_L\)时,有电流从输出端流入,称为输出高电平电流\(I_{OH}\),也称为拉电流

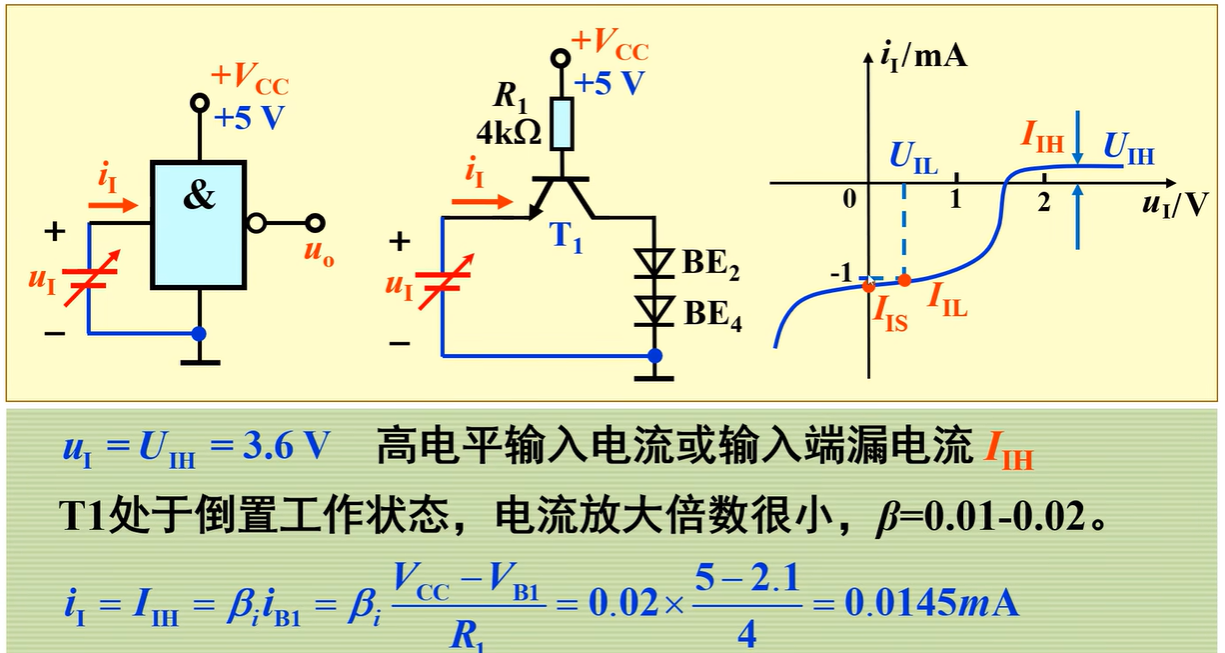

倒置放大的\(\beta\)是很小的,一般只有0.01或者0.02的样子

若无D,此时\(T_3\)是可以导通的,电路将不能实现正常的逻辑运算

TTL与非门的电气特性¶

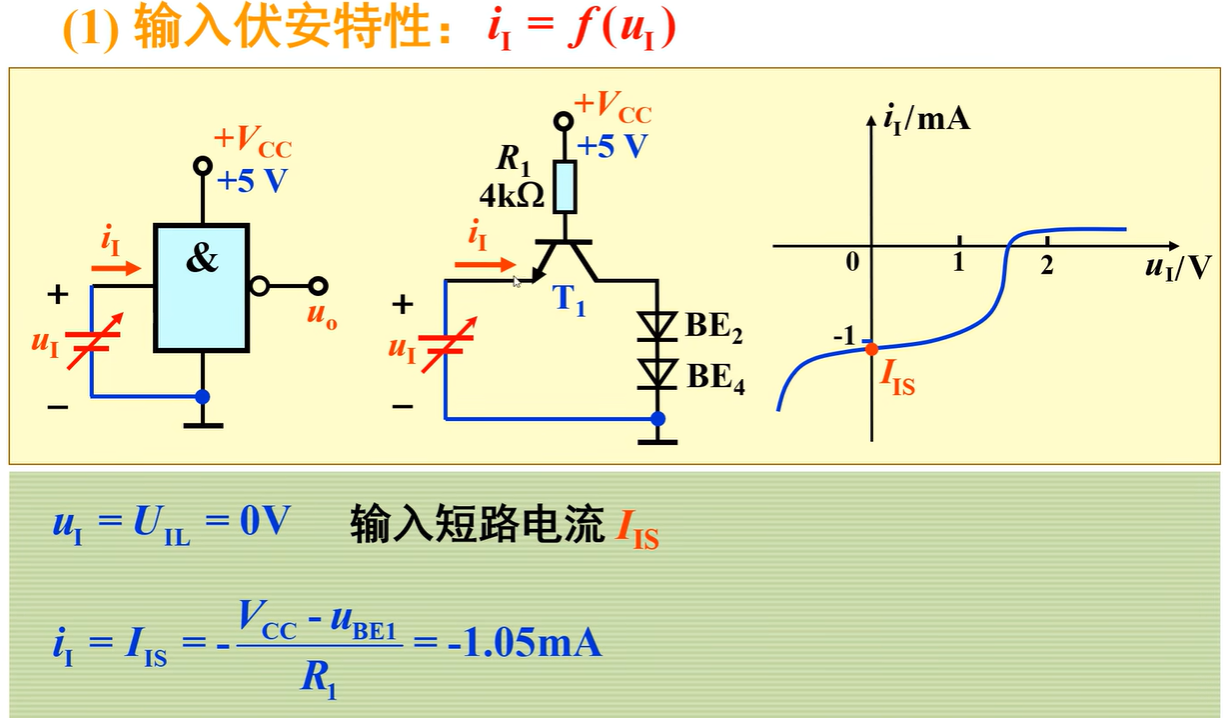

输入伏安特性¶

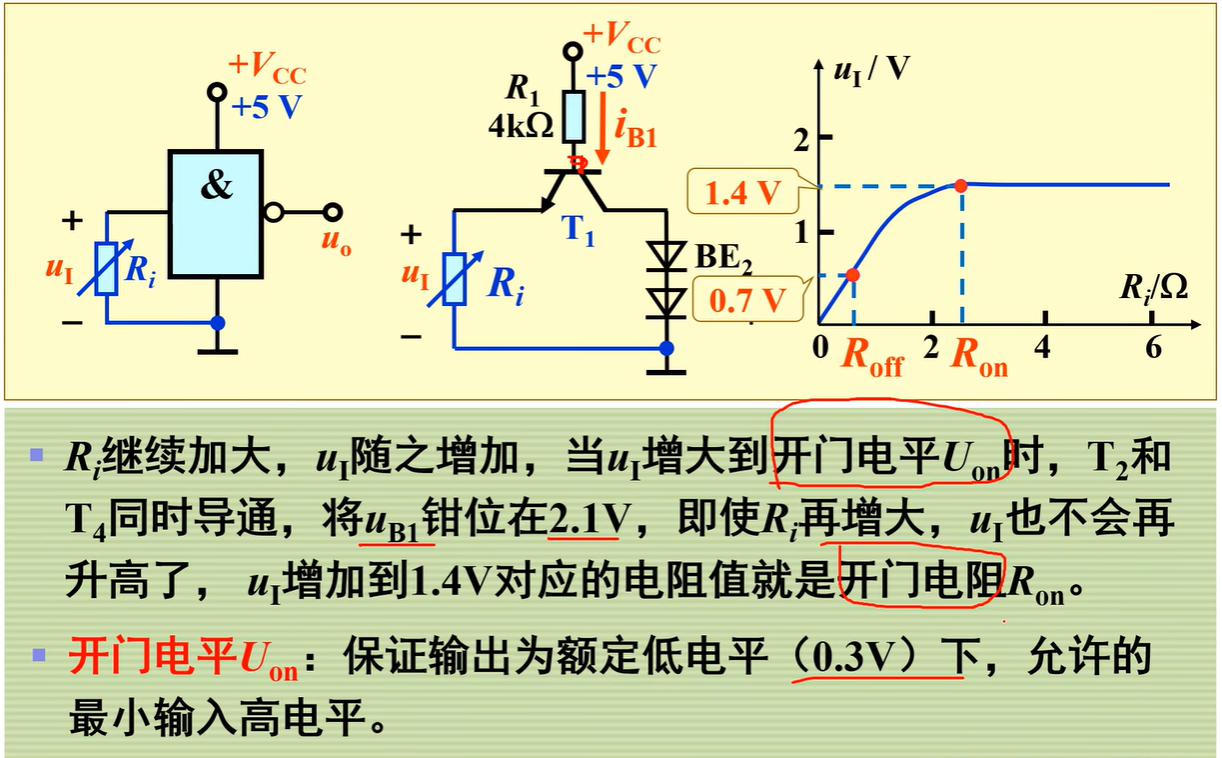

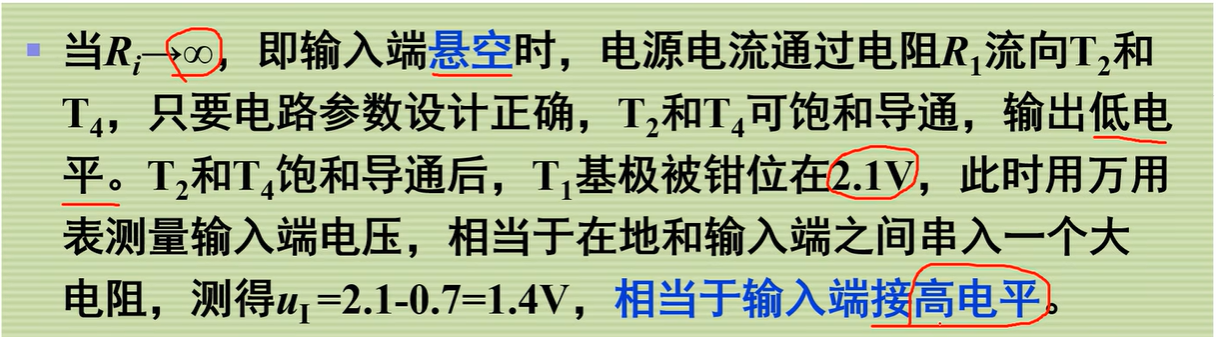

输入端负载特性¶

说明TTL与非门有输入端不用时,需要进行处理,不然就相当于悬空接入了一个高电平

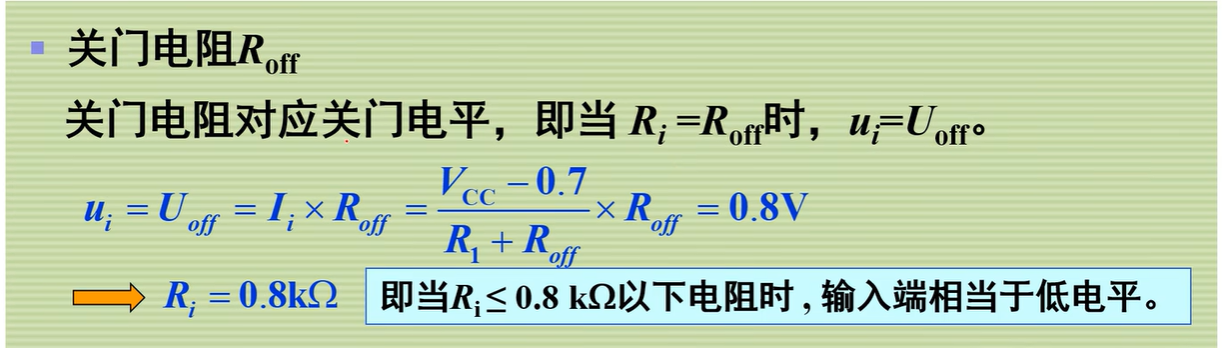

注:他这里关门电平\(U_{off}\)是按0.8V来算的(实际上应该差不多都可以)

注:他这里开门电平\(U_{ON}\)是按照2V来算的,留了一些裕量

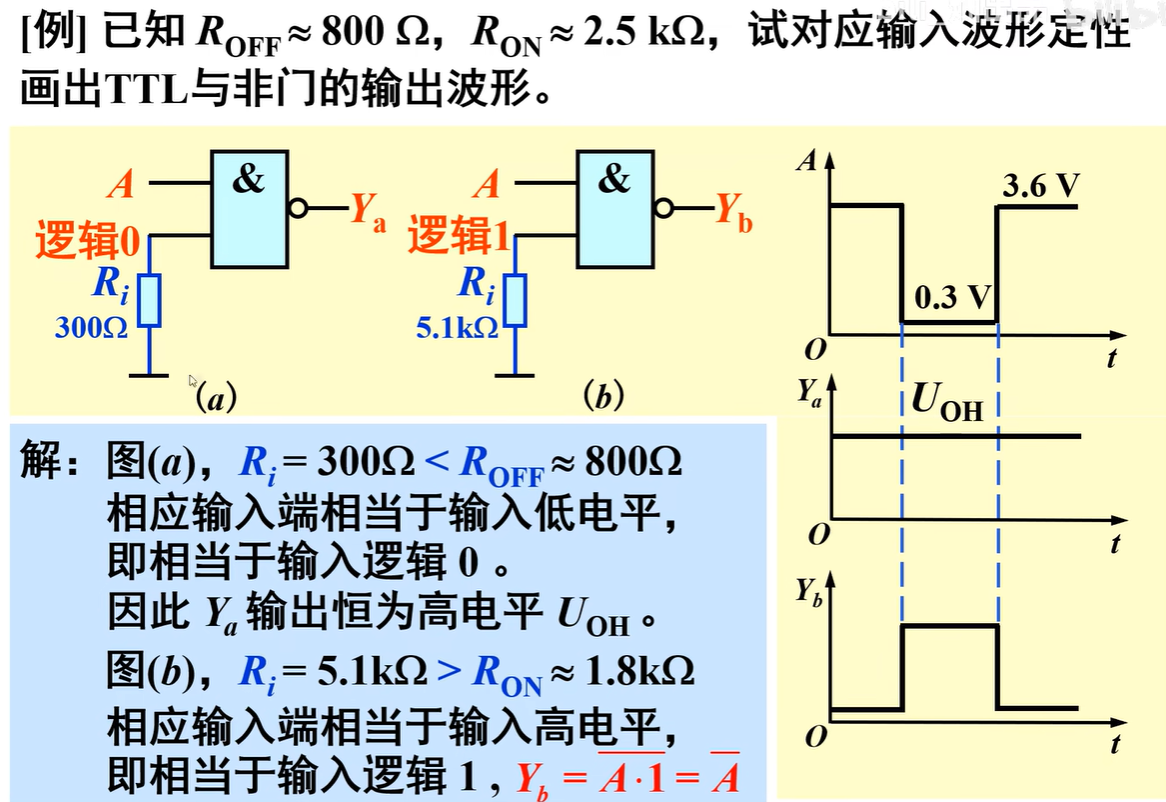

其实主要就是要明白关门电阻和开门电阻的含义

- 接入的\(R_i\)小于\(R_{OFF}\),则输入为逻辑0

- 接入的\(R_i\)大于\(R_{ON}\),则输入为逻辑 1

- 什么都不接,悬空的,也为逻辑 1

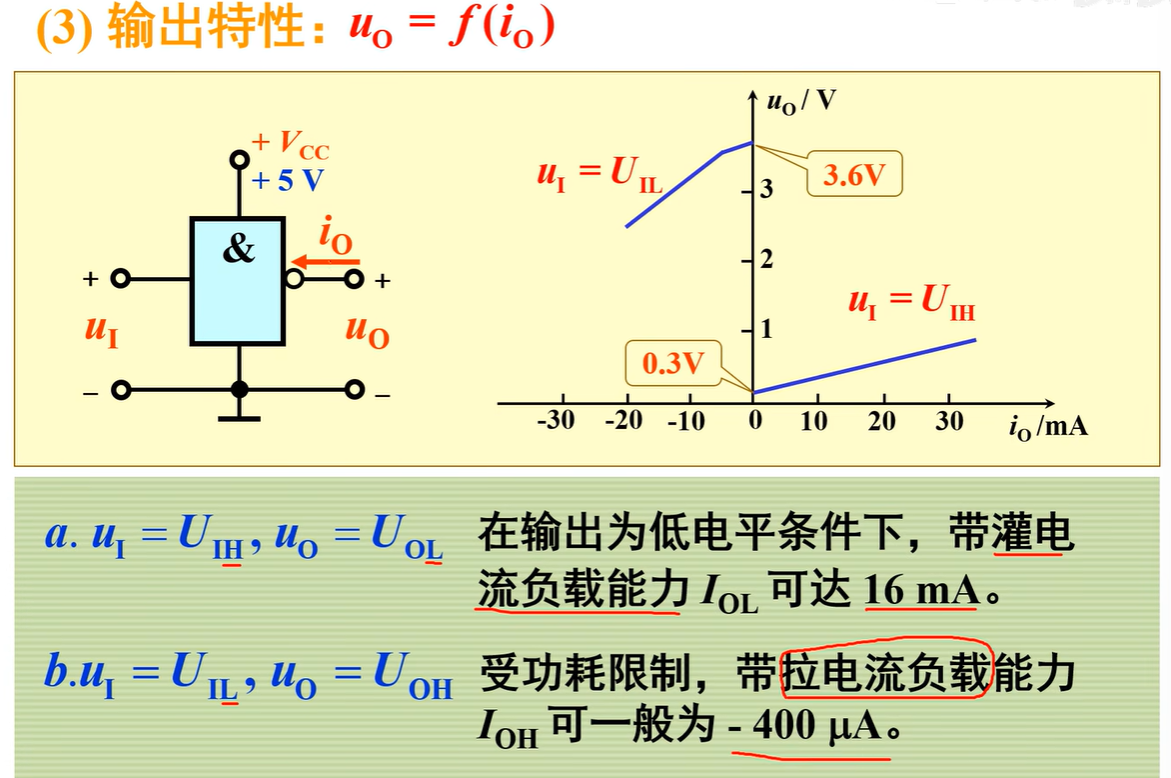

输出特性¶

注意:输出短路电流\(I_{OS}\)可达\(-33mA\),将造成器件过热烧毁,故门电路输出端不能接地

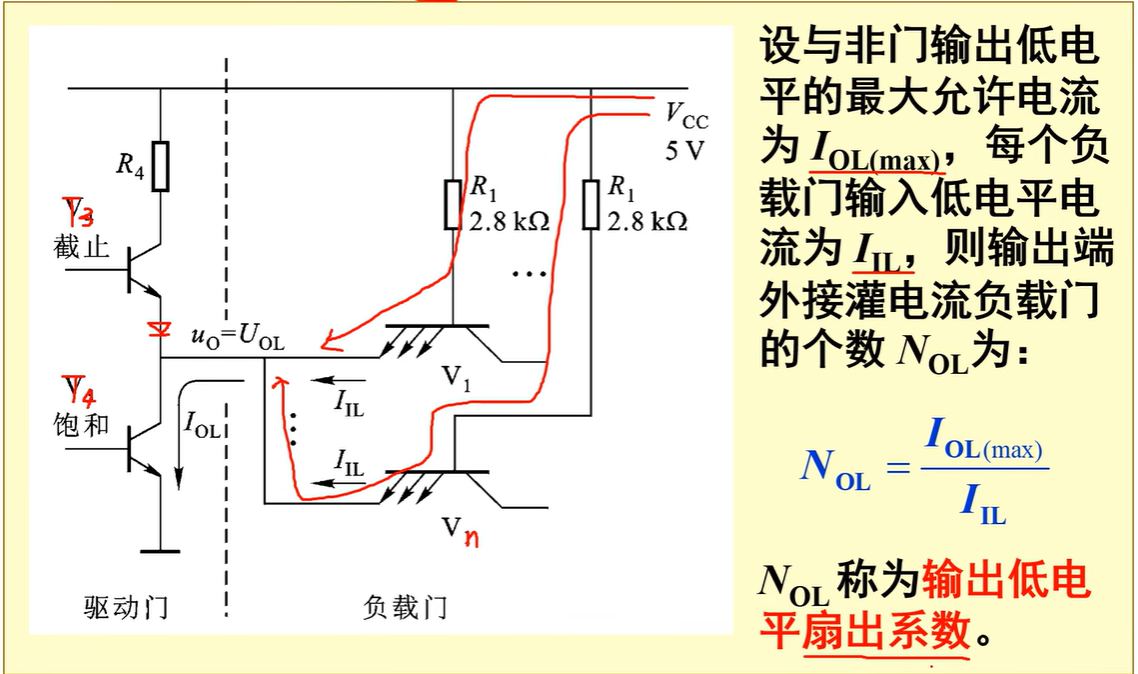

灌电流负载¶

外接负载电流流入与非门的输入端的负载。与非门输出低电平\(U_{OL}\)时,带灌电流负载

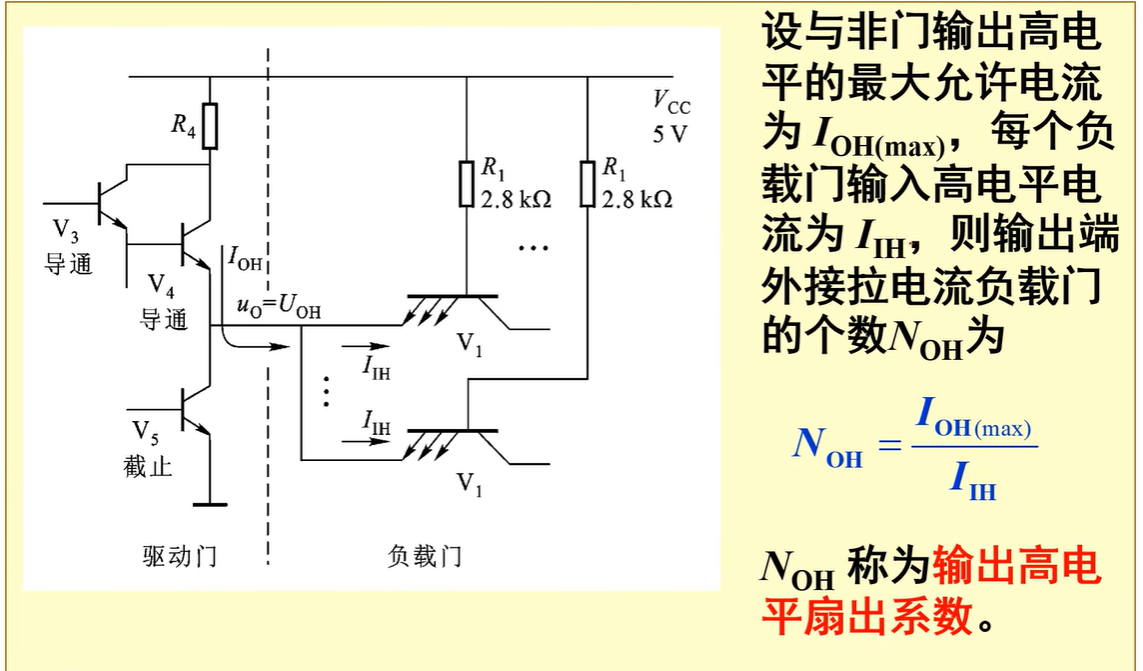

拉电流负载¶

负载电流从与非门的输出端流向外接负载门的负载。与非门输出高电平\(U_{OH}\)时,带拉电流负载

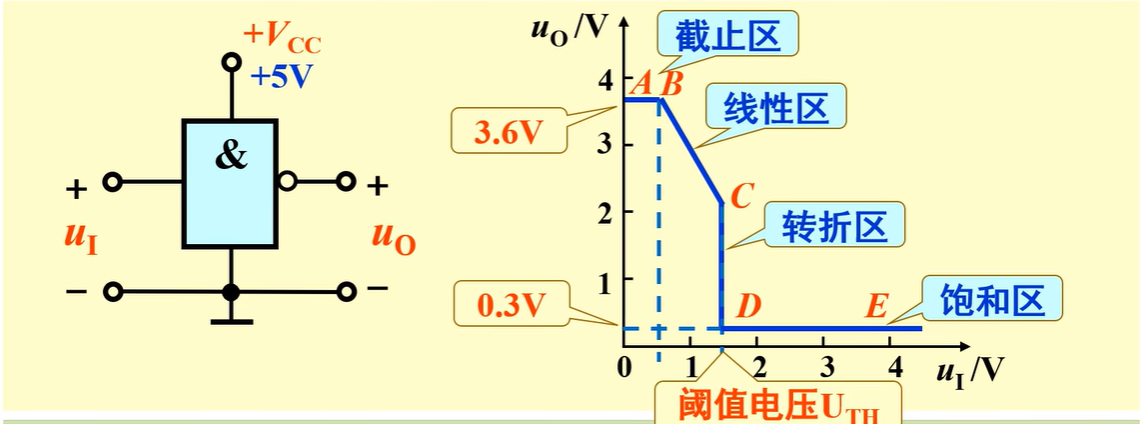

电压传输特性¶

AB段(截止区):

- \(u_I<0.5V\),\(u_{B1}<1.2V\)

- \(T_{2}\)、\(T_4\)截止,\(T_3\)、\(D\)导通

- \(u_O=U_{OH}=3.6V\)

BC段(线性区):

- \(u_I>0.6V\Rightarrow u_{B1}\uparrow\)

- \(T_{2}\)开始导通(放大区),\(T_4\)仍截止

- \(u_{I}\uparrow \Rightarrow u_O \downarrow\)(线性)

CD段(转折区):

- \(u_I \uparrow \rightarrow 1.4V \Rightarrow T_4\)开始导通\(\Rightarrow u_O \downarrow \downarrow\)

- 输出电压会急剧下降为低电平0.3V

- 与非门的阈值电压(或门槛电压)\(U_{TH}=1.4V\)

DE段(饱和区):

- \(u_I>1.4V\)

- \(T_2\)、\(T_4\)饱和导通,\(T_3\)、\(D\)截止

- \(u_O=U_{OL} \le 0.3V\)

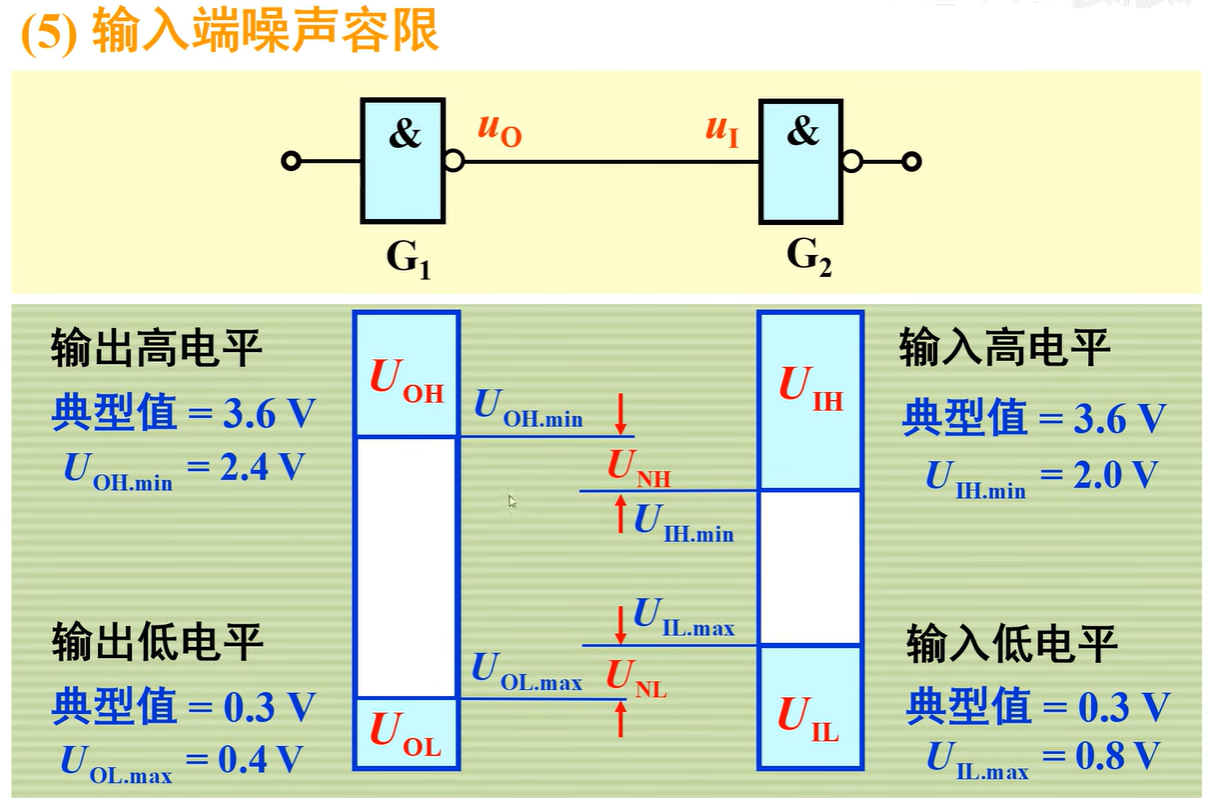

输入端噪声容限¶

\(G_2\)输入高电平时的噪声容限:

- \(U_{NH}\)——允许叠加的负向噪声电压的最大值

- \(U_{NH}=U_{OH.min}-U_{IH.min}=0.4V\)

\(G_2\)输入低电平时的噪声容限:

- \(U_{NL}\)——允许叠加的正向噪声电压的最大值

- \(U_{NL}=U_{IL.max}-U_{OL.max}=0.4V\)

其他类型的TTL门电路¶

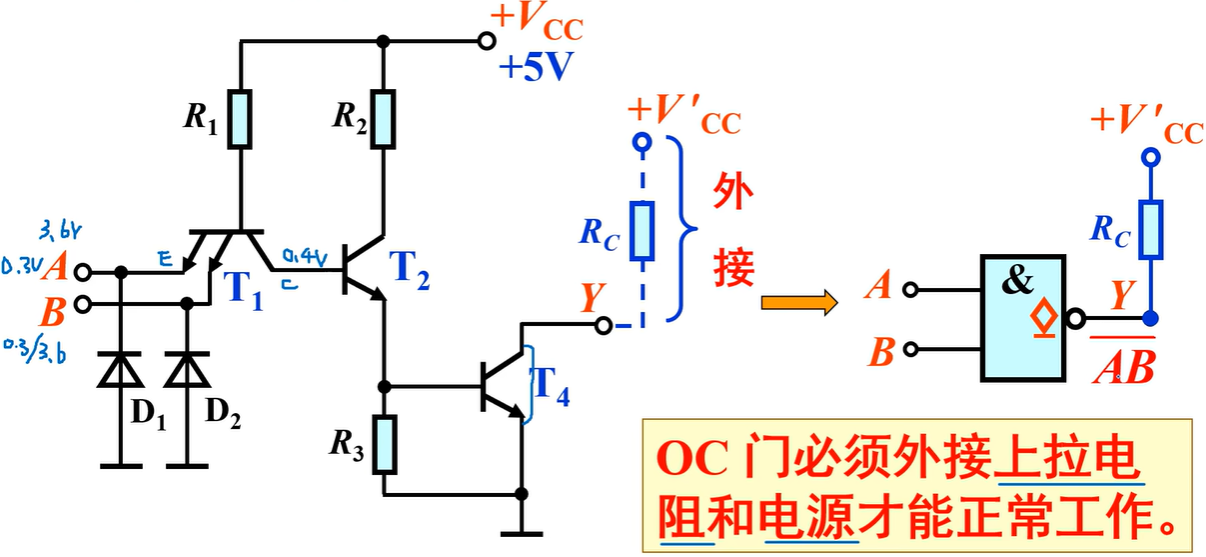

集电极开路与非门(OC门)¶

即 Open Collector Gate 简称OC门

注:为什么要上拉电阻和电源?因为和原本普通的TTL门电路不同,当A和B至少有一个0时,\(T_4\)断开,但是输出要为 1,原先TTL门电路是可以由上方的\(V_{CC}\)供电,但是OC门不行,故需要外接电流和上拉电阻

OC门的应用¶

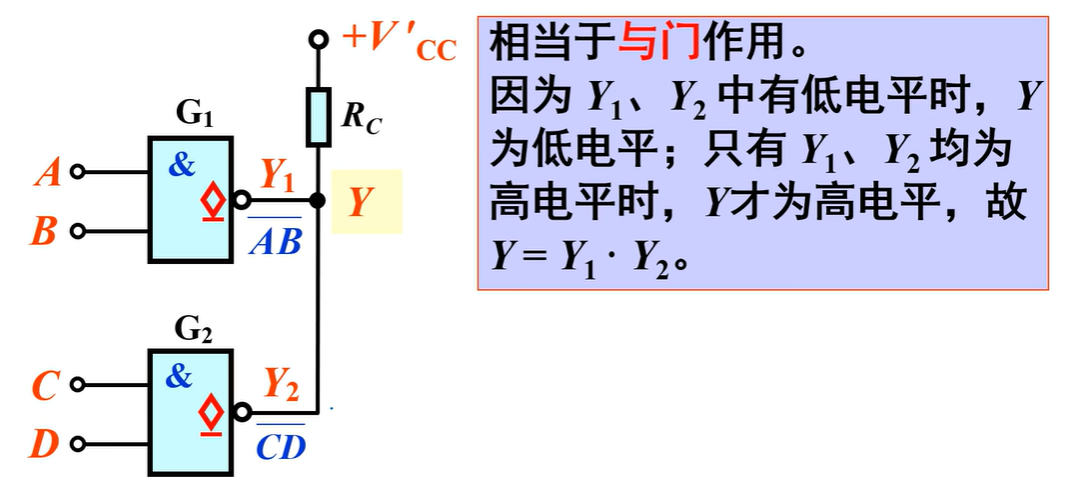

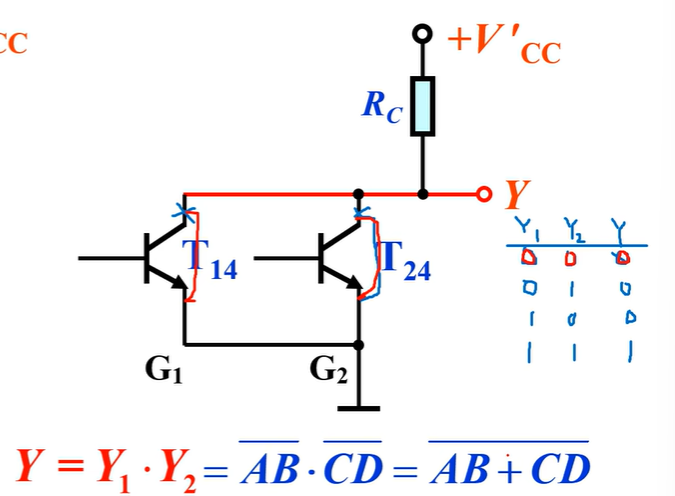

- 实现“线与”逻辑

两个或多个OC门的输出端直接相连,相当于将这些输出信号相与,称为线与

注:普通的TTL门电路这样接相当于把输出端短路,电流很大足以烧坏门电路;故普通的TTL与非门是不能把输出端接在一起实现“线与”的功能的

这两个OC门的局部等效电路

主要就是因为OC门的高电平是由上拉电阻和电源提供的,所以不会出现普通的TTL门电路那种短路烧坏的情况

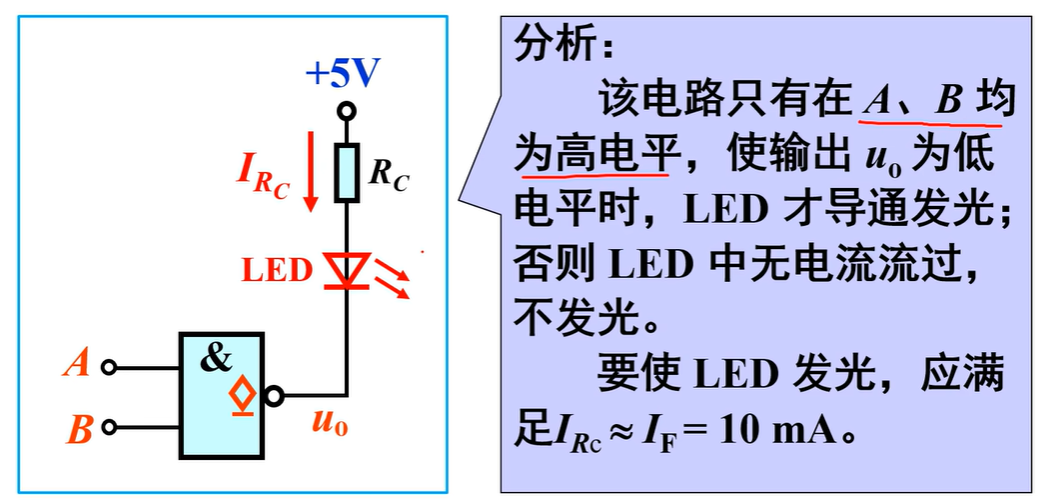

- 驱动发光二极管

对于普通的TTL门电路,只能采用“灌电流”的方式驱动发光二极管,因为如果采用“拉电流”的方式驱动,则电流是不够大的(只有\(400\mu A\),达不到10mA,忘了回前面看看)

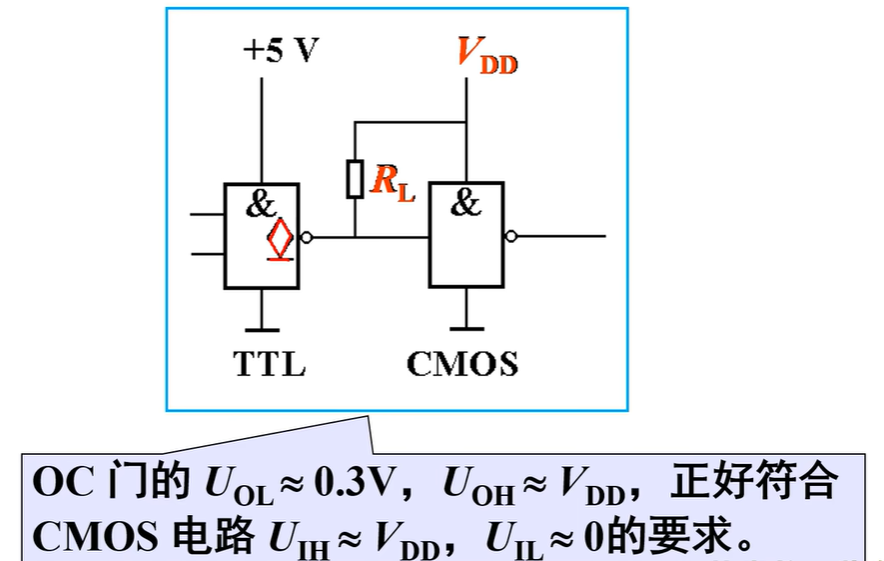

- 实现电平转换

TTL与非门有时需要驱动其他种类门电路,而不同种类门电路的高低电平标准不一样(一般的TTL门电路,工作电压在5V左右;而CMOS门电路的工作电压比较高一些3-15V,一般门电路是无法高过输出电压的,但假如驱动的门电路要求电压为12V,就没办法了)

应用OC门就可以适应负载门对电平的要求(OC门输出的高低电平是由外接的电源\(V_{DD}\)以及上拉电阻\(R_L\)决定的)

三态门(TSL门)¶

即 Three-State Logic 门,简称TSL门

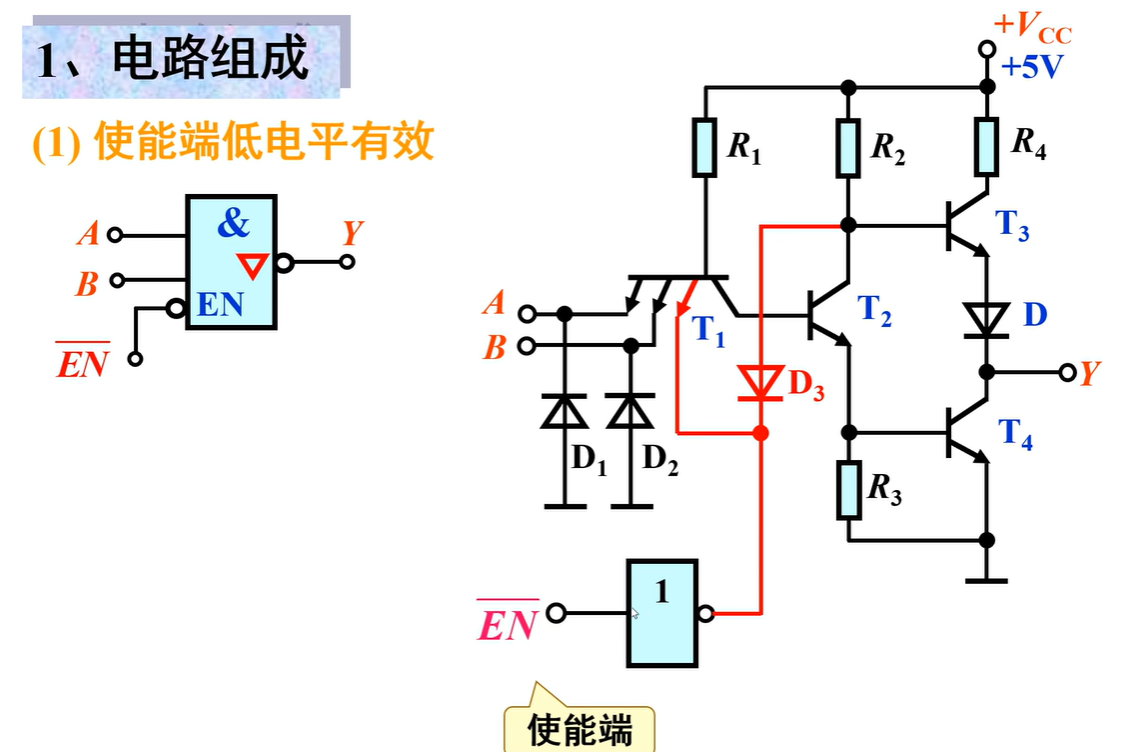

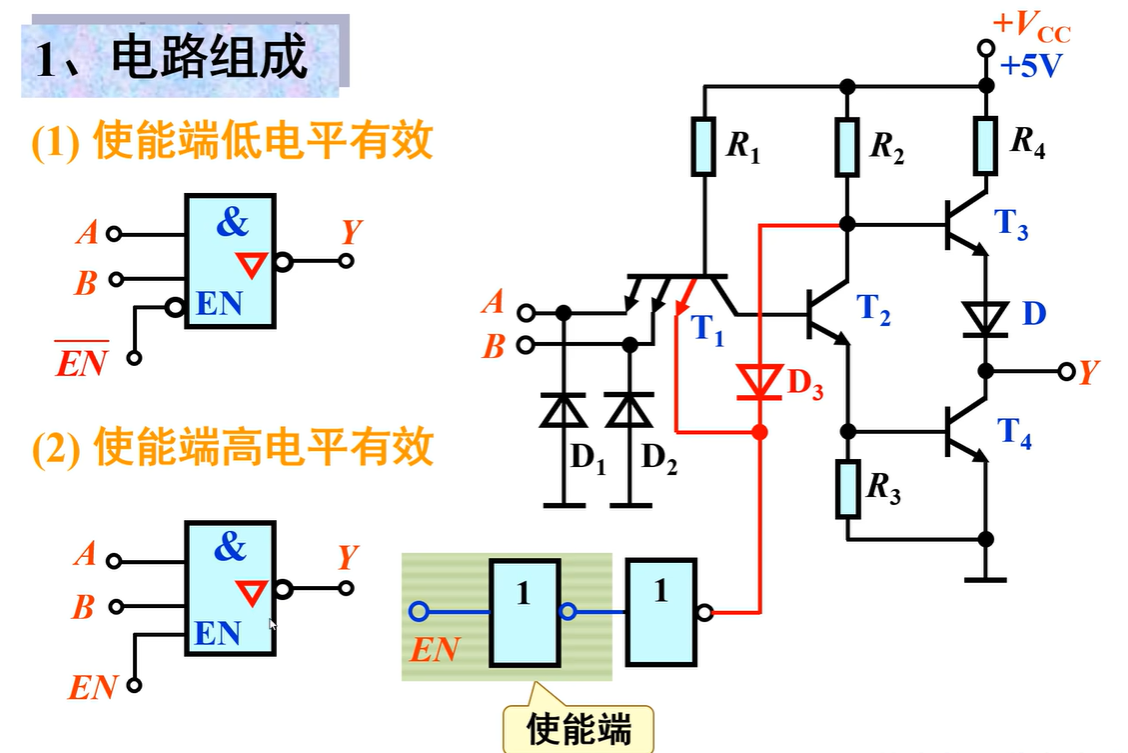

电路结构¶

其实把标红色的部分拿掉,就和前面学过的TTL门电路是一样的

- 使能端低电平有效

使能端\(EN\)有非号即代表低电平有效,无非号则为高电平有效

而EN其实就是Enable的意思,作用即让门电路处于工作状态or静止状态

- 使能端高电平有效

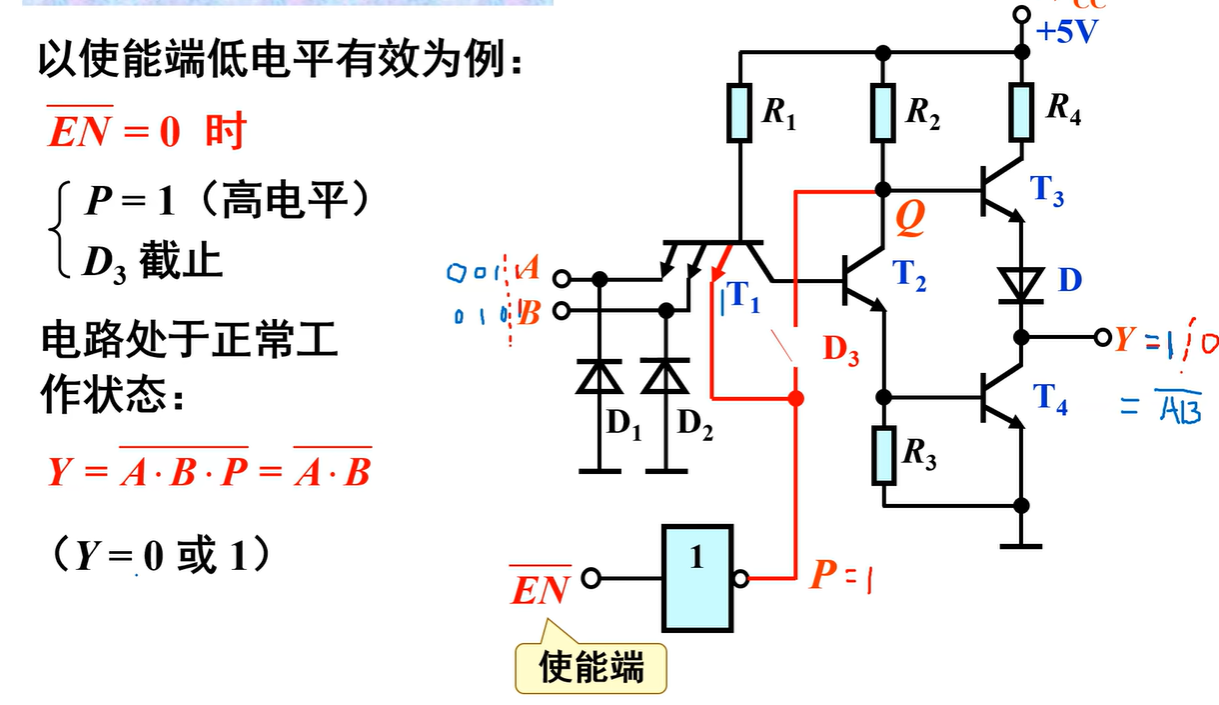

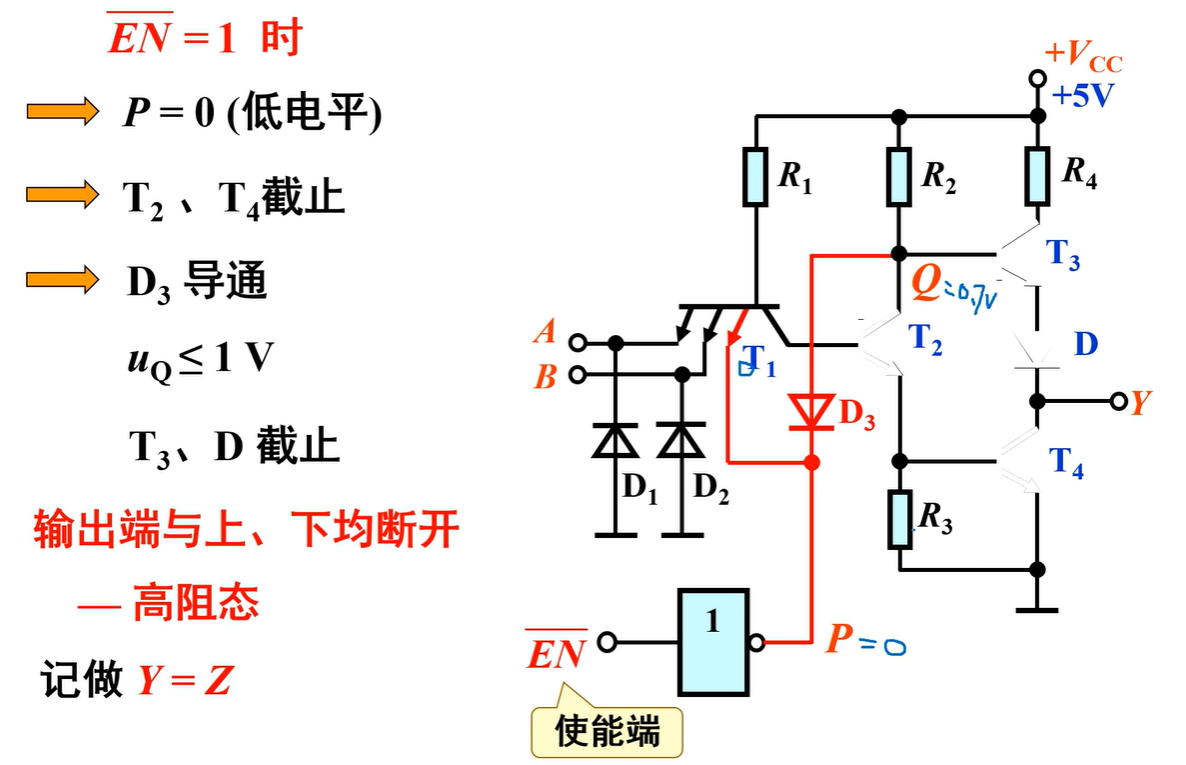

工作原理¶

- 正常的与非门状态

- 高阻状态

其实就是因为P等于0电位了,加上二极管\(D_3\)的存在,导致了Q点的电位被“钳制”在了\(0.7V\),不能和正常一样让\(T_3\)导通了,此时Y既不能和“地”相连,也不能和\(V_{CC}\)相连,故将这种状态称为“高阻状态”

三态门的应用¶

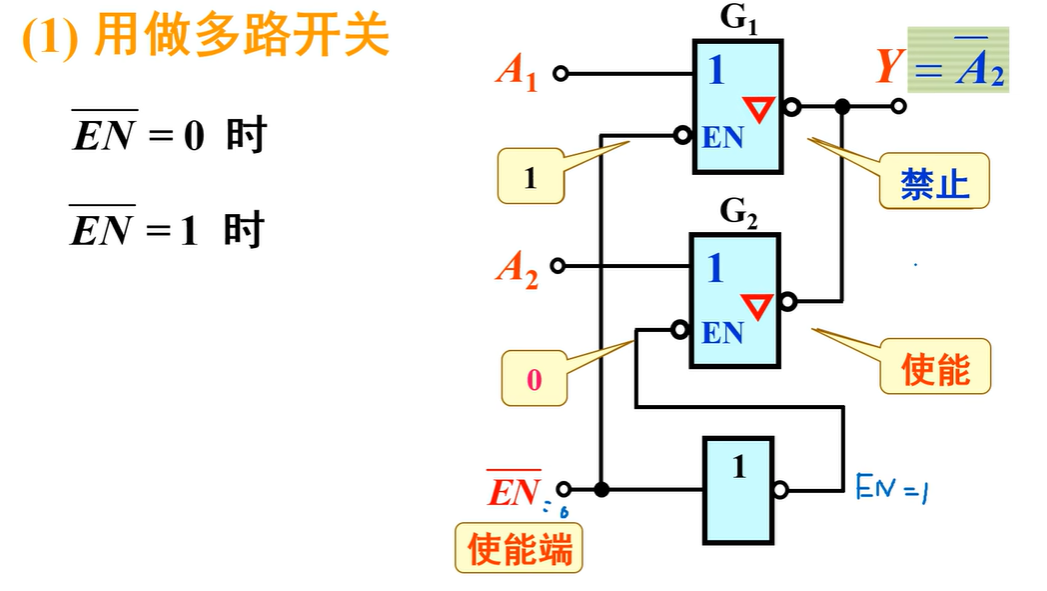

- 用作多路开关

注:写了“1”而没有用“&”符号说明三态门只有一个输出

\(\bar{EN}=0\)时,\(G_1\)使能,\(G_2\)禁止,\(Y=\bar {A_1}\)

\(\bar{EN}=1\)时,\(G_2\)使能,\(G_1\)禁止,\(Y=\bar {A_2}\)

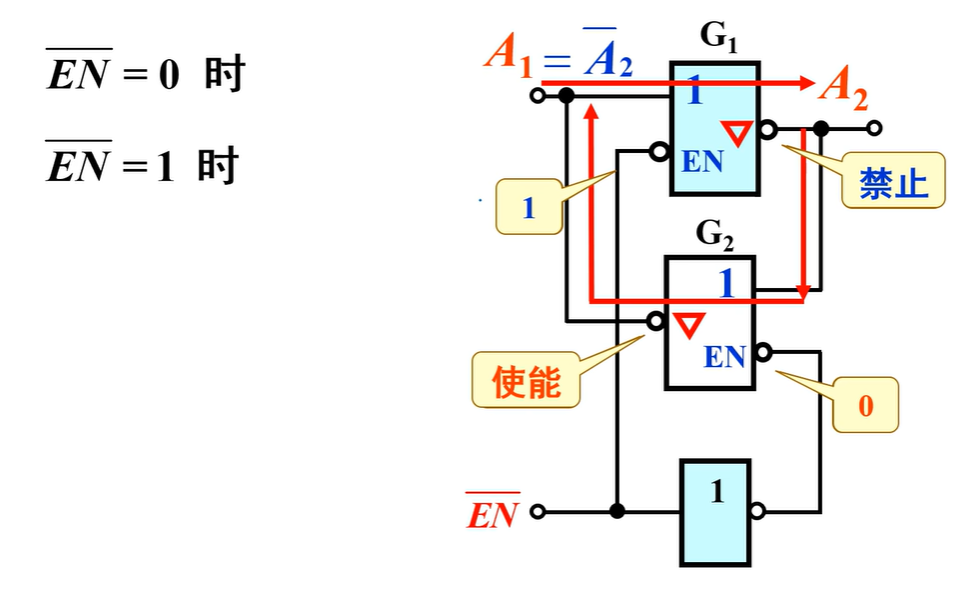

- 用于信号双向传输

\(\bar{EN}=0\)时,\(G_1\)使能,\(G_2\)禁止,则信号从\(A_1\)取反后传递到\(A_2\)

\(\bar{EN}=1\)时,\(G_2\)使能,\(G_1\)禁止,则信号从\(A_2\)取反后传递到\(A_1\)

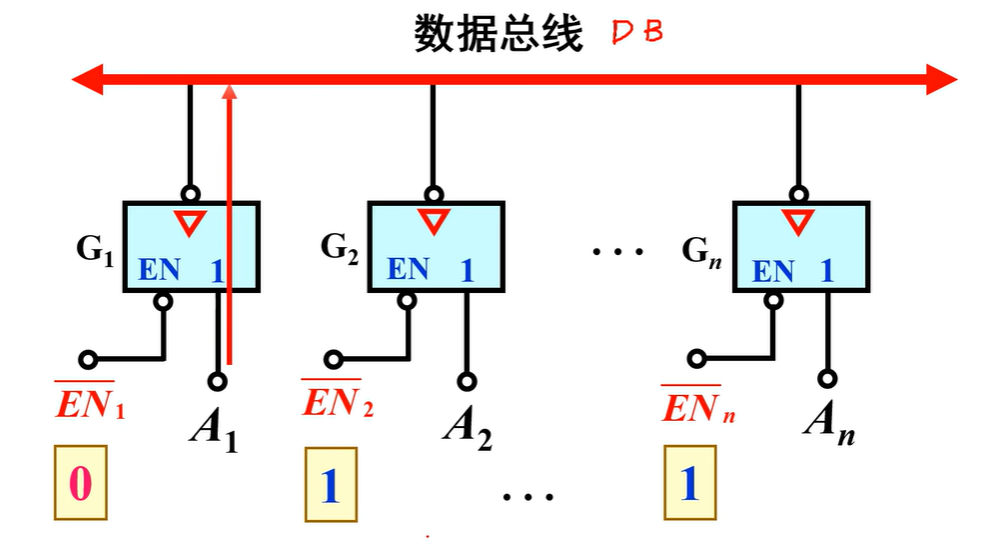

- 构成数据总线(Data Bus)

当使能端\(\bar{EN_1}=0\)其他都为 1 时,就能让\(A_1\)取反后送到数据线传输

其他也是同理,但是注意:前提是任何时刻,只允许某一个三态门使能,其他三态门都为高阻状态

TTL集成门电路芯片¶

54系列和74系列¶

74系列民用,54系列军用

具有完全相同的电路结构和电气性能参数,但54系列更适合在温度条件恶劣、供电电源变化大的环境中工作

TTL逻辑门电路各子系列的性能比较¶

向高速发展¶

- 74系列(即标准TTL)

- 74H系列(即高速TTL,简称HTTL)

- 74S系列(即肖特基TTL,简称STTL)

- 74AS系列(即先进肖特基TTL,简称ASTTL)

肖特基二极管的特性

- 导通压降只有0.4V,比一般二极管(0.7V)小

- 一般的PN结都有电容效应,而肖特基二极管没有

- TTL门电路中加入肖特基三极管可以使得三极管饱和深度没那么深,从而使三级管脱离饱和区过渡到截止区的速度会更快(所谓的更高速度也就是在这)

向低功耗发展¶

- 74系列(即标准TTL)

- 74L系列(即低功耗TTL,简称LTTL)

向减小功耗、延迟发展¶

- 74系列(即标准TTL)

- 74LS系列(即低功耗肖特基TTL,简称LSTTL)【应用最广泛的】

- 74ALS系列(即先进低功耗肖特基TTL,简称ALSTTL)

在不同的子系列TTL中,器件型号后面几位数字相同时,通常逻辑功能、外型尺寸、外引线排列都相同。但工作速度(平均传输延迟时间\(t_{pd}\))和平均功耗不同。实际使用时,高速门电路可以替换低速的,反之不行

比如00就代表与非门,04代表非门,08代表与门,32代表或门,86代表异或门

TTL集成门电路的使用注意事项¶

输出端的连接¶

普通的TTL门电路输出端不允许直接并联使用(一个门输出高电平,另一个门输出低电平,就会造成短路烧坏门电路)

三态输出门的输出端可以并联使用,但同一时刻只能有一个门工作,其他门输出处于高阻状态

集电极开路门输出端可并联使用,但公共输出端和电源\(V_{CC}\)之间应接上拉电阻\(R_C\)

输出端不允许直接接电源\(V_{CC}\)或者直接接地,输出电流应小于产品手册上规定的最大值

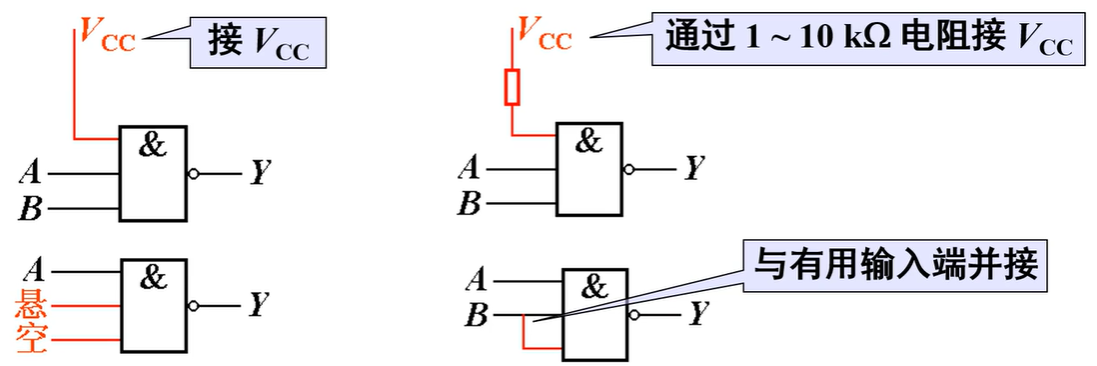

闲置输入端的处理¶

- 与门和与非门

与门和与非门的多余输入端接入逻辑 1或者与有用输入端并接

与有用输入端并联:在上例中,\(B\cdot B\)还是\(B\),故不影响,但是在这样的接法下要考虑分流,需要看输入信号够不够大,分成两个后还是高电平才使用这种方法连接,所以这种接法在平时的使用中较少

TTL电路输入端悬空相当于接入逻辑 1高电平,做实验时与门和与非门等的多余输入端可悬空,但实际使用中多余输入端一般不悬空,防止干扰

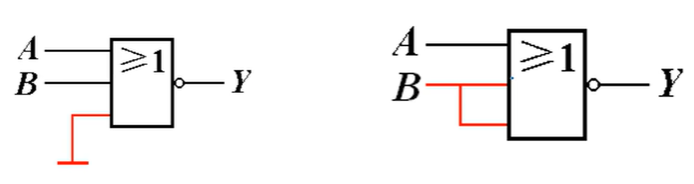

- 或门和或非门

或门和或非门的多余输入端接入逻辑 0或者与有用输入端并接

与有用输入端并联:在上例中,\(B+B\)还是\(B\),故不影响,但是也一样要考虑驱动电流的分流

电源电压及电源干扰的消除¶

54系列电源电压应满足\(5V\pm 10\%\),74系列电源电压应满足\(5V\pm 5\%\)

为防止动态尖峰电流或脉冲电流通过公共电源内阻耦合到逻辑电路造成干扰,需对电源进行滤波

电路安装接线和焊接应注意的问题¶

连线尽量要短,最好用绞合线;整体接地要好,地线要粗而短

焊接用的电烙铁不大于25W,焊接时间要短;焊接完毕后,只能用少许酒精清洗